カスタムASICを作るにはどうしたら良いか

Google Edge TPU

Google が開発したエッジでのAI推論用の ASIC がある。

https://cloud.google.com/edge-tpu?hl=ja

これは、chisel で開発されたみたい。

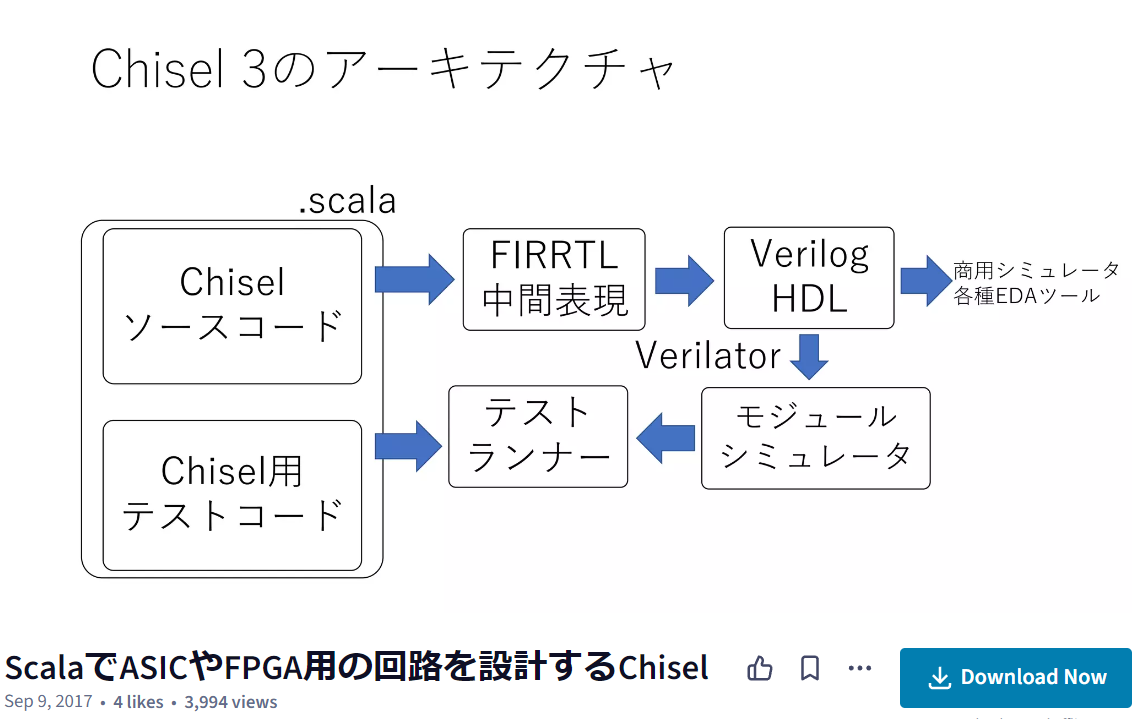

ハードウェア構築言語 Chisel がアツい(かもしれない)(出典:Hatena Blog) - KUMICO

GoogleのEdge TPUの論理回路がChiselという言語で開発されたという内容。AIとは直接関係ない話なんですが、FPGAやASICの論理設計といえば、もう20年前からずっとVerilog-HDLかVHDLという言語と相場が決まっていたもので、Chiselが使われたということは(ごく一部では)驚きをもって迎えられています。

Chiselで始める爆速LSI設計 - VVVVVVVVVVVVLSI

このサイトの内容は勉強になった。Chisel から GDSII ファイルを生成している。

ASICの設計

EDA ツールというのを用いる。

実際に半導体製造を請け負う企業に依頼する場合は、その企業から PDK と呼ばれる開発キットを購入する必要がある。

例えばTSMCは車載IC向けの7nm製造プロセスに最適化したPDKを提供しており、車載ICの設計を行うメーカーがTSMCの7nmプロセスを利用してチップを製造したい場合は、このPDKを購入して設計を行うというわけです。

https://gigazine.net/news/20200711-google-skywater-opensource-pdk/

チップを製造するには?

OpenMPW というのがある。

MPW = Multi Project Wafer,つまり1枚のウェハ上に複数の設計を載せるということです.シャトルサービスと言うこともあります.従来のLSI設計はNDA (秘密保持契約) を締結して PDK (Process Development Kit) を入手し,商用EDAツールを使って設計する必要がありましたが,PDKとEDAをオープンソースにしたのが大きな違いです.

https://note.com/akira_tsuchiya/n/nae2c5e569c27

OpenLANE という、OSS のツールチェーンを用いて設計が可能みたい。

GDSII ストリーム出力

半導体業界では、レイアウトデータを受け渡すための標準フォーマットとして、GDS-II形式(Streamデータとも呼ばれる)が利用されている。従って、VDECや半導体メーカにデータを送るときは、GDS-IIに変換する必要がある。

http://jaco.ec.t.kanazawa-u.ac.jp/edu/micro1/lab/06.html

参考資料

Zero to ASIC Course | Zero to ASIC Course

半導体設計界隈では有名なコースみたい。

【大原雄介の半導体業界こぼれ話】GlobalFoundries、無償でカスタムASICが作れるOpen Source Silicon Initiativeに参加 - PC Watch

https://www.slideshare.net/KeiNakazawa/scalaasicfpgachisel